Our mission

Transistors are the building blocks of digital integrated circuits found in every modern electronic device, from cell phones to industrial electronics. However, more and more emerging applications utilise ultra-low power sources and operate at low power in harsh environmental conditions where transistors cannot perform efficiently.

In ZeroAMP, we will address the societal and industrial needs for such computation solutions by pushing beyond the limits of transistors. To tackle this challenge, we will develop novel nanoelectromechanical (NEM) switches that survive extreme environments.

In ZeroAMP, we will address the societal and industrial needs for such computation solutions by pushing beyond the limits of transistors. To tackle this challenge, we will develop novel nanoelectromechanical (NEM) switches that survive extreme environments.

Novel zero-leakage NEM switches

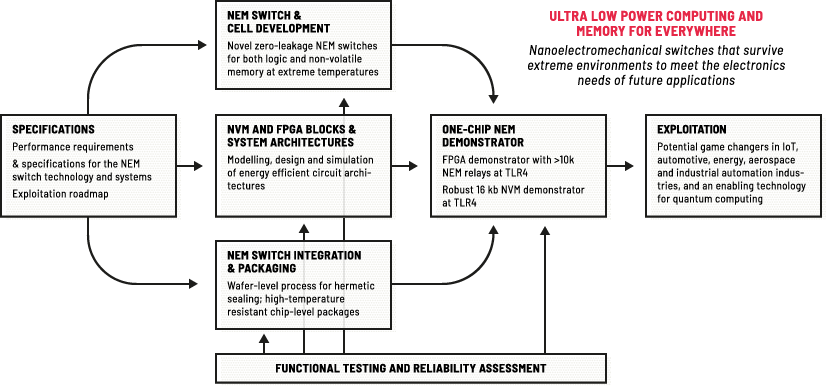

Our strategies

In ZeroAMP, we aim to build electronic components comprising logic and non-volatile memory (NVM) to meet the needs of emerging applications that require reliable operation in extreme environments while maintaining a very high energy efficiency.

For this purpose, we will develop novel zero-leakage NEM switches based on a novel 4-terminal (4-T) relay and a novel moment-driven bistable circular relay. By combining novel energy-efficient circuit architectures with new materials, we will reduce device count and eliminate leakage in both logic and memory at all operational temperatures (at near cryogenic temperature and up to 300°C).

For this purpose, we will develop novel zero-leakage NEM switches based on a novel 4-terminal (4-T) relay and a novel moment-driven bistable circular relay. By combining novel energy-efficient circuit architectures with new materials, we will reduce device count and eliminate leakage in both logic and memory at all operational temperatures (at near cryogenic temperature and up to 300°C).

Further on, we will develop a novel ultra-high-density 3D stacking technology for the large-scale integration of the NEM switching elements on a multi-layer interconnect stack. We will also implement a wafer-level process for hermetic sealing of the NEM switches to ensure long-term reliability as well as high-temperature resistant chip-level packages for the circuit demonstrators.

Finally, we will demonstrate an energy-efficient FPGA for harsh environments validated in a laboratory environment (Technology Readiness Level 4 TRL-4) with >10k NEM relays, based on the 4-T and bistable switches in the same die, to produce efficient, reprogrammable logic structures that retain their state when switched off. Furthermore, we will build a robust 16 kb NVM demonstrator, based on the novel bistable NEM relay, for which one-time programmable (OTP) memory and reprogrammable memory will be targeted.

Finally, we will demonstrate an energy-efficient FPGA for harsh environments validated in a laboratory environment (Technology Readiness Level 4 TRL-4) with >10k NEM relays, based on the 4-T and bistable switches in the same die, to produce efficient, reprogrammable logic structures that retain their state when switched off. Furthermore, we will build a robust 16 kb NVM demonstrator, based on the novel bistable NEM relay, for which one-time programmable (OTP) memory and reprogrammable memory will be targeted.

Energy-efficient processors with zero standby power

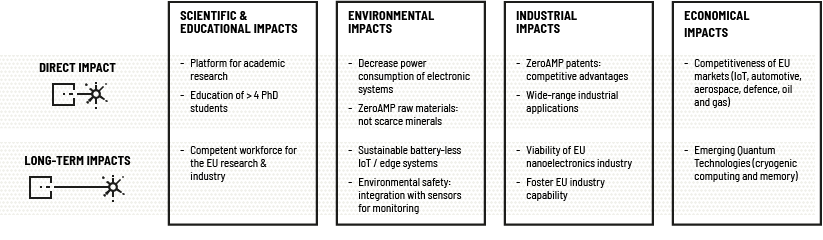

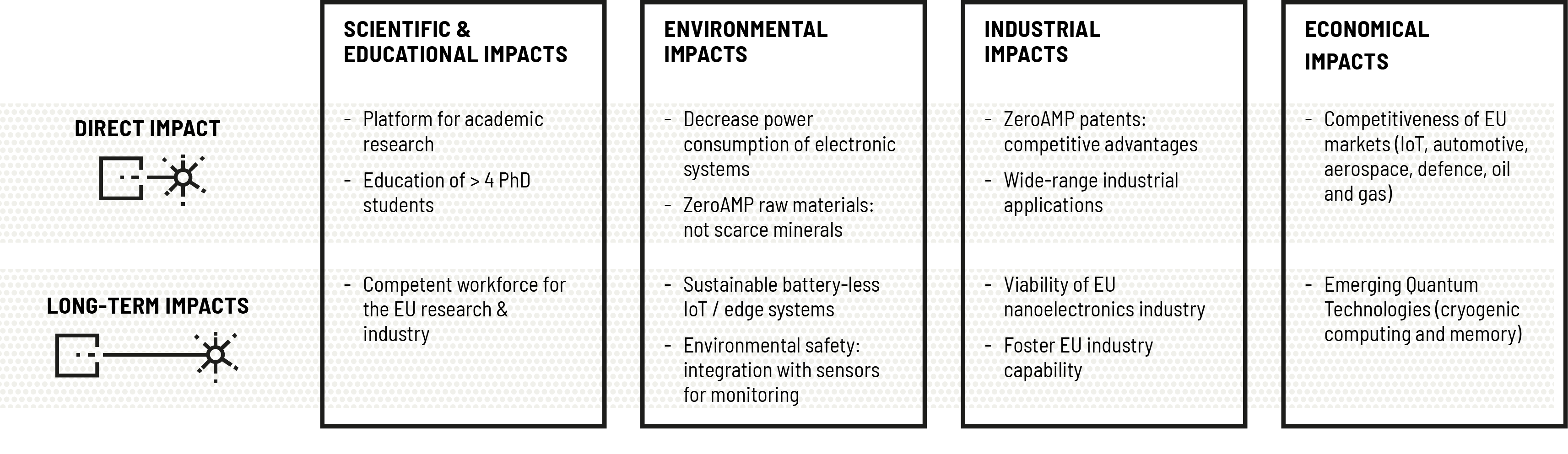

The future exploitation and applications

Autonomous nodes in the IoT require extremely energy-efficient processors with zero standby power, while all-electric vehicles and more-electric aircraft need electronics controllers that work at very high temperatures. At the other end of the spectrum, readout circuitry for superconducting quantum circuits need to operate close to cryogenic temperatures.

Thus, our ZeroAMP technology will be potential game-changers in the IoT, automotive, energy, aerospace and industrial automation industries, as well as an enabling technology for cryogenic quantum computing.

Background publications

Nanoelectromechanical Devices

| S. Rana, J. Mouro, S. J. Bleiker, J. D. Reynolds, H. M. Chong, F. Niklaus, and D. Pamunuwa, “Nanoelectromechanical relay without pull-in instability for high-temperature non-volatile memory,” Nature communications, vol. 11, no. 1, pp. 1-10, 2020. [Online]. [ bib | DOI | http ] |

| J. Mouro, S. Rana, J. Reynolds, H. Chong, and D. Pamunuwa, “Estimating the surface adhesion force using pull-in/-out hysteresis in comb-drive devices,” in Proc. Int. Conf. Solid-State Sensors, Actuators and Microsystems & Eurosensors XXXIII (TRANSDUCERS & EUROSENSORS XXXIII). IEEE, 2019, pp. 1981-1984. [ bib ] |

| J. D. Reynolds, S. Rana, J. Mouro, D. Pamunuwa, and H. M. H. Chong, “4-terminal lateral mems silicon relay with nanocrystalline graphite contact and polymer insulating mechanical coupler,” in Proc. Int. Conf. Solid State Devices and Materials, 2019. [ bib ] |

| S. Rana, J. D. Reynolds, T. Y. Ling, M. S. Shamsudin, S. H. Pu, H. M. Chong, and D. Pamunuwa, “Nano-crystalline graphite for reliability improvement in MEM relay contacts,” Carbon, vol. 133, pp. 193-199, 2018. [Online]. [ bib | DOI | http ] |

| J. D. Reynolds, S. Rana, Y. L. Ting, L. A. Boodhoo, S. H. Pu, D. Pamunuwa, and H. M. H. Chong, “Nanocrystalline graphite coatings for lateral silicon MEMS transistors,” in Proc. International Conference on Micro and Nano Engineering (MNE), Sep. 2017. [ bib ] |

| L. Boodhoo, S. Rana, J. Reynolds, Y. Tsuchiya, W. Redman-White, S. H. Pu, H. Mitzuta, D. Pamunuwa, and H. M. H. Chong, “Nano-crystalline graphite coated SOI NEMS switches,” in Proc. Int. Microprocesses and Nanotechnology Conf., 2016. [ bib ] |

Materials and nanofabrication

| S. Kataria, S. Wagner, and M. C. Lemme, “Scalable growth of two-dimensional materials-a prerequisite for process integration,” ECS Transactions, vol. 80, no. 4, p. 259, 2017. [ bib ] |

| S. Kataria, S. Wagner, T. Cusati, A. Fortunelli, G. Iannaccone, H. Pandey, G. Fiori, and M. C. Lemme, “Growth-induced strain in chemical vapor deposited monolayer MoS2: Experimental and theoretical investigation,” Advanced Materials Interfaces, vol. 4, no. 17, p. 1700031, 2017. [ bib ] |

| S. Kataria, S. Wagner, J. Ruhkopf, A. Gahoi, H. Pandey, R. Bornemann, S. Vaziri, A. D. Smith, M. Ostling, and M. C. Lemme, “Chemical vapor deposited graphene: From synthesis to applications,” physica status solidi (a), vol. 211, no. 11, pp. 2439-2449, 2014. [ bib ] |

High-density heterogenous integration and packaging

| X. Wang, S. J. Bleiker, P. Edinger, C. Errando-Herranz, N. Roxhed, G. Stemme, K. B. Gylfason, and F. Niklaus, “Wafer-level vacuum sealing by transfer bonding of silicon caps for small footprint and ultra-thin MEMS packages,” Journal of microelectromechanical systems, vol. 28, no. 3, pp. 460-471, 2019. [ bib ] |

| A. C. Fischer, F. Forsberg, M. Lapisa, S. J. Bleiker, G. Stemme, N. Roxhed, and F. Niklaus, “Integrating MEMS and ICs,” Microsystems & Nanoengineering, vol. 1, no. 1, pp. 1-16, 2015. [ bib ] |

| M. Lapisa, G. Stemme, and F. Niklaus, “Wafer-level heterogeneous integration for MOEMS, MEMS, and NEMS,” IEEE Journal of Selected Topics in Quantum Electronics, vol. 17, no. 3, pp. 629-644, 2011. [ bib ] |

Circuit and System Architectures

| T. Qin, S. J. Bleiker, S. Rana, F. Niklaus, and D. Pamunuwa, “Performance analysis of nanoelectromechanical relay-based field-programmable gate arrays,” IEEE Access, vol. 6, pp. 15997-16009, 2018. [Online]. [ bib | DOI | http ] |

| S. Rana, Q. Tian, A. Bazigos, D. Grogg, M. Despont, C. L. Ayala, C. Hagleitner, A. M. Ionescu, R. Canegallo, and D. Pamunuwa, “Energy and latency optimization in NEM relay-based digital circuits,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 61, no. 8, pp. 2348-2359, Aug. 2014. [ bib | DOI ] |

Modelling, Design Methods and Tools

| I. Marozau, M. Auchlin, V. Pejchal, F. Souchon, D. Vogel, M. Lahti, N. Saillen, and O. Sereda, “Reliability assessment and failure mode analysis of MEMS accelerometers for space applications,” Microelectronics Reliability, vol. 88, pp. 846-854, 2018. [ bib ] |

| T. Qin, S. Rana, and D. Pamunuwa, “Design methodologies, models and tools for very-large-scale integration of NEM relay-based circuits,” in Proc. IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Nov. 2015, pp. 641-648. [ bib | DOI ] |

| S. Rana, Q. Tian, A. Bazigos, D. Grogg, M. Despont, C. L. Ayala, C. Hagleitner, A. M. Ionescu, R. Canegallo, and D. Pamunuwa, “Energy and latency optimization in NEM relay-based digital circuits,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 61, no. 8, pp. 2348-2359, Aug. 2014. [ bib | DOI ] |

| A. Bazigos, C. L. Ayala, M. Fernandez-Bolanos, Y. Pu, D. Grogg, C. Hagleitner, S. Rana, T. T. Qin, D. Pamunuwa, and A. M. Ionescu, “Analytical compact model in Verilog-A for electrostatically actuated ohmic switches,” IEEE Transactions on Electron Devices, vol. 61, no. 6, pp. 2186-2194, Jun. 2014. [ bib | DOI ] |

| A. Bazigos, C. L. Ayala, S. Rana, D. Grogg, M. Fernandez-Bolaños, C. Hagleitner, T. Qin, D. Pamunuwa, and A. M. Ionescu, “Electromechanical design space exploration for electrostatically actuated ohmic switches using extended parallel plate compact model,” Solid-State Electronics, vol. 99, pp. 93-100, 2014. [Online]. [ bib | DOI | http ] |

| S. Rana, T. Qin, D. Grogg, M. Despont, Y. Pu, C. Hagleitner, and D. Pamunuwa, “Modelling NEM relays for digital circuit applications,” in Proc. IEEE International Conference on Circuits and Systems (ISCAS), May 2013, pp. 805-808. [ bib | DOI ] |

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 871740 (ZeroAMP).